Debido a un problema con el estimador de energía inicial (EPE) para Intel® Stratix® 10 dispositivos versión 19.4 y versiones anteriores, es posible que vea este error incluso si todavía hay pines disponibles cuando se utilizan pines de entrada diferencial y los voltajes VINDEX de todos los bancos de E/S no son de 2,5 V.

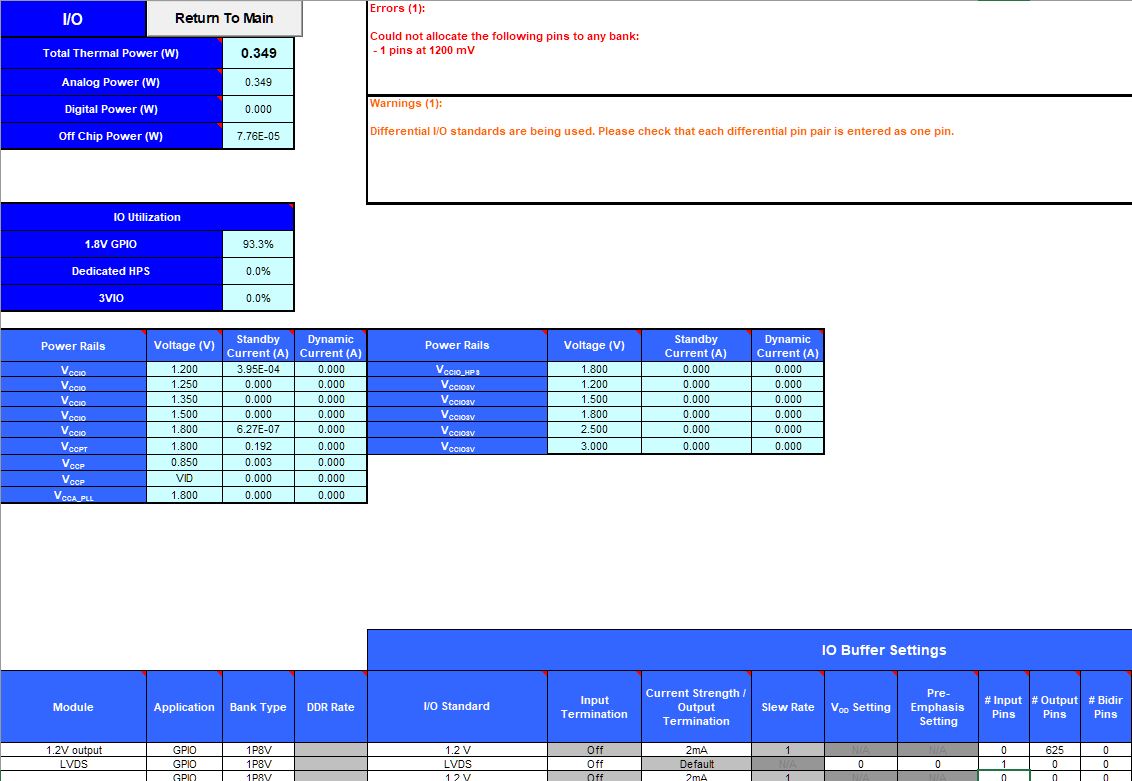

Aquí tiene un ejemplo.

- Dispositivo: 1SG280H

- Paquete: F50

- Cantidad de E/S del usuario: 672

- Número de banco de E/S: 14

- Cantidad de pines previos al banco de E/S: 48

- Uso de E/S del usuario:

- Salida de 1.2 V * 625 pines

- Entrada LVDS * 1 par

En este caso, dado que se utilizan 625 pines para una salida de 1,2 V, los voltajes V SOLICITAR de 14 bancos de E/S son de 1,2 V.

La entrada LVDS está impulsada por VCCPT, no por V LW. Por lo tanto, se debe poder asignar un par de entradas LVDS a los pines restantes. Pero el EPE para Intel Stratix 10 dispositivos muestra incorrectamente un error como la siguiente imagen.

Puede ignorar este error de forma segura.

Este problema se corrige a partir del EPE para Intel Stratix 10 dispositivos del software Intel® Quartus® Prime Pro Edition versión 21.3.